# WD3138

# White LED Driver with Digital and PWM Brightness Control in Tiny Package

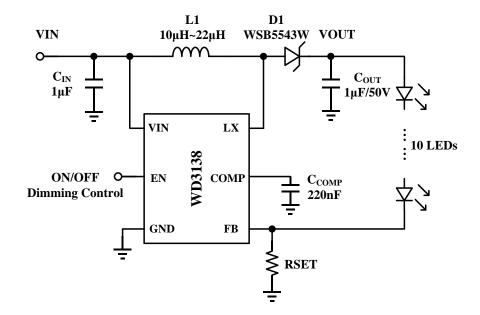

With a 40-V rated integrated power switch MOSFET, the WD3138 is a boost converter that drives up to 10 White LEDs in series. The WD3138 operates at 600kHz fixed switching frequency to reduce output ripple, improve conversion efficiency, and allows for the use of small external components.

The default Full-Scale White LED current is set by an external sensor resistor with regulated 200mV feedback voltage, as shown in typical application. During operation, the LED current can be controlled using the 1-wire digital interface through EN pin. Alternately, a Pulse Width Modulation (PWM) signal can also be applied on the EN pin, through which the PWM Duty-Cycle determines the feedback reference voltage and then the White LED current. In either 1-Wire digital or PWM mode, the WD3138 does not burst the LED current; therefore, it does not generate audible noises on the ceramic output capacitor. For maximum protection, the device features integrated open LED protection that disables the WD3138 to prevent the output voltage from exceeding the absolute maximum ratings during open LED conditions.

The WD3138 is available in a PCB space saving DFN 2mm x 2mm-6L Package with bottom thermal pad. Standard product is Pb-free and Halogen-free.

### Features

- 2.7V~5.5V Input voltage range

- 38V Open LED Protection

- 200mV Reference Voltage

- 600kHz Switching frequency

- Up to 91% Efficiency

- Flexible Digital and PWM Brightness Control

- PWM Dimming Duty ranges from 1% to 100%

- Built-in Soft-Start and Over-Current limit

Http//:www.sh-willsemi.com

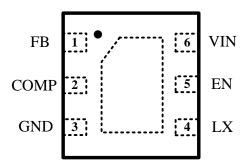

DFN 2mm x 2mm-6L Pin configuration (Top view)

|      | Marking       |

|------|---------------|

| B38D | = Device Code |

| Y    | = Year Code   |

| W    | = Week Code   |

### **Order information**

| Device       | Package    | Shipping       |  |

|--------------|------------|----------------|--|

| WD3138D-6/TR | DFN-2x2-6L | 3000/Reel&Tape |  |

## **Applications**

- Smart Phones

- Tablets

- Portable games

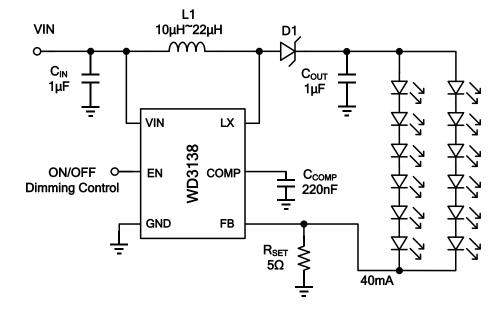

# **Typical applications**

# **Pin descriptions**

| Symbol      | Pin No.  | Descriptions                                                             |

|-------------|----------|--------------------------------------------------------------------------|

| FB          | 1        | Feedback pin for LED current. Connect the sense resistor from FB to      |

| ГВ          | 1        | GND                                                                      |

| COMP        | 2        | Output of the Error Amplifier. Connect an external capacitor to this pin |

| CONF        | 2        | to compensate the converter                                              |

| GND         | 3        | Ground                                                                   |

| LX          | 4        | Switch pin. Connect the inductor between VIN and LX. This pin is also    |

|             | 4        | used to sense output voltage for Open LED Protection                     |

| EN          | Б        | Enable pin of boost converter. It also can be used for PWM and digital   |

|             | 5        | dimming control                                                          |

| VIN         | 6        | Power supply. Connect VIN to a supply voltage between 2.7V and $5.5V$    |

| Thermal Pad | Bottom   | The exposed thermal pad should be soldered to the analog ground          |

|             | BULLUITI | plane. If possible, use the thermal via to connect to ground plane       |

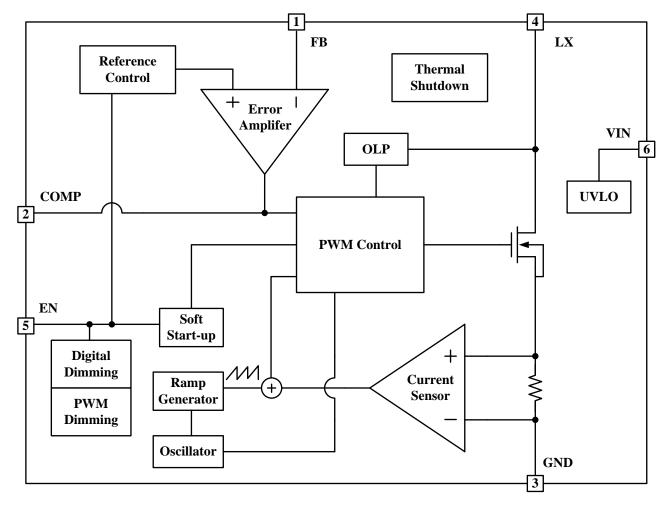

# **Block diagram**

### Absolute maximum ratings

| Parameter                                                    | Symbol           | Value                | Unit |

|--------------------------------------------------------------|------------------|----------------------|------|

| VIN pin voltage range                                        | V <sub>IN</sub>  | -0.3~6.5             | V    |

| EN, FB, COMP pin voltage range                               | -                | -0.3~V <sub>IN</sub> | V    |

| LX pin voltage range (DC)                                    | -                | -0.3~40              | V    |

| Power Dissipation – DFN-2x2-6L (Note 1)                      | р                | 1.5                  | W    |

| Power Dissipation – DFN-2x2-6L (Note 2)                      | P <sub>D</sub>   | 0.7                  | W    |

| Junction to Ambient Thermal Resistance – DFN-2x2-6L (Note 1) | R <sub>θJA</sub> | 65                   | °C/W |

| Junction to Ambient Thermal Resistance – DFN-2x2-6L (Note 2) |                  | 140                  | °C/W |

| Junction temperature                                         | TJ               | 160                  | °C   |

| Lead temperature(Soldering, 10s)                             | TL               | 260                  | °C   |

| Operation temperature                                        | Topr             | -40 ~ 85             | °C   |

| Storage temperature                                          | Tstg             | -55 ~ 150            | °C   |

These are stress ratings only. Stresses exceeding the range specified under "Absolute Maximum Ratings" may cause substantial damage to the device. Functional operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure to extreme conditions may affect device reliability.

**Note 1:** Surface mounted on JEDEC high-k Board using 1 square inch pad size, multilayer board with 1-ounce internal power and ground planes and 2-ounce copper trances on top and bottom of the board. **Note 2:** Surface mounted on JEDEC low-k Board using 1 square inch pad size, two-layer board with 2-ounce copper traces on top of the board.

# $\label{eq:Electronics Characteristics} \mbox{ (Ta=25°C, V_{IN}=3.6V, V_{EN}=V_{IN}, C_{IN}=C_{OUT}=1 \mu \mbox{F, unless otherwise noted)}}$

| Parameter                    | Symbol                 | Test Conditions                             | Min  | Тур | Max | Unit       |

|------------------------------|------------------------|---------------------------------------------|------|-----|-----|------------|

| Supply Current               | •                      |                                             |      |     |     |            |

| Operation Voltage Range      | V <sub>IN</sub>        |                                             | 2.7  |     | 5.5 | V          |

| Under Voltage Lockout        | V <sub>UVLO</sub>      | V <sub>IN</sub> Rising                      | 1.8  | 2.2 | 2.5 | V          |

| UVLO Hysteresis              | V <sub>UVLO-HYS</sub>  |                                             |      | 0.1 |     | V          |

| Quiescent Current            | l <sub>Q</sub>         | No Switching                                |      | 0.4 | 1   | mA         |

| Supply Current               | I <sub>S</sub>         | Switching                                   |      | 1   | 2   | mA         |

| Shutdown Current             | I <sub>SD</sub>        | V <sub>EN</sub> < 0.4V                      |      |     | 1   | μA         |

| Enable and Reference Contro  |                        |                                             |      |     |     |            |

|                              | V <sub>ENL</sub>       |                                             |      |     | 0.4 | V          |

| EN Threshold Voltage         | V <sub>ENH</sub>       |                                             | 1.5  |     |     | V          |

| EN Pull-down Resistance      | R <sub>EN</sub>        |                                             |      | 800 |     | kΩ         |

| EN Shutdown Pulse Width      | t <sub>OFF</sub>       | EN High to Low                              | 2.5  |     |     | ms         |

| 1-wire Digital Brightness    |                        | EN Pin Low,                                 | 000  |     |     |            |

| Detection Time               | t <sub>1W_DET</sub>    | Note 1                                      | 260  |     |     | μS         |

| 1-wire Digital Brightness    |                        |                                             | 100  |     |     | _          |

| Detection Delay              | t <sub>1W_DELAY</sub>  |                                             | 100  |     |     | μS         |

| 1-wire Digital Brightness    |                        |                                             |      |     |     |            |

| Detection Window Time        | t <sub>1W_WIN</sub>    |                                             | 1    |     |     | ms         |

| Voltage and Current Control  | •                      |                                             |      |     |     |            |

|                              |                        | 100% Full Scale                             | 196  | 200 | 204 | mV         |

| Feedback Reference           | V <sub>REF</sub>       | 1% Dimming                                  |      | 2   |     | mV         |

| Feedback Input Bias Current  | I <sub>FB</sub>        |                                             |      |     | 2   | μA         |

| Operation Frequency          | f <sub>OSC</sub>       |                                             | 500  | 600 | 700 | kHz        |

| Maximum Duty Cycle           | D <sub>MAX</sub>       |                                             | 92   | 95  |     | %          |

| PWM Dimming Clock Rate       |                        | Recommended                                 | 5    |     | 100 | KHz        |

| PWM Dimming Duty Cycle       |                        | Recommended                                 | 1    |     | 100 | %          |

| Power Switch                 | •                      |                                             |      |     |     |            |

| On Resistance                | R <sub>ON</sub>        | VIN=3.6V                                    |      | 0.6 |     | Ω          |

| N-channel Leakage Current    | I <sub>LN_NFET</sub>   | V <sub>LX</sub> =40V, T <sub>A</sub> =25 °C |      |     | 1   | μA         |

| OC and OLP                   | •                      |                                             |      |     |     |            |

| 0                            | I <sub>LIM</sub>       |                                             | 0.68 | 0.8 |     | Α          |

| Current Limit                | I <sub>LIM_START</sub> | Start-up                                    |      | 0.4 |     | Α          |

| Open LED Protection          |                        | LED Open,                                   |      |     | 40  | V          |

| Threshold                    | V <sub>OLP</sub>       | Measured on LX                              | 36   | 38  | 40  |            |

| 1-wire Digital Timing        |                        | ı d                                         |      |     |     |            |

| Start Time of Program Stream | t <sub>START</sub>     |                                             | 2    |     |     | μS         |

| End Time of Program Stream   | t <sub>EOS</sub>       |                                             | 2    |     | 360 | μ <b>S</b> |

| Start Time of Data-Byte      |                        |                                             |      |     |     | · · ·      |

| Stream                       | t <sub>SOD</sub>       |                                             | 2    |     | 360 | μS         |

| High Time Low Bit            | t <sub>H_LB</sub>      | Logic 0                                     | 2    |     | 180 | μS         |

| Low Time Low Bit           | t <sub>L_LB</sub>    | Logic 0                   | 2xt <sub>H_LB</sub> |     | 360 | μS |

|----------------------------|----------------------|---------------------------|---------------------|-----|-----|----|

| High Time High Bit         | t <sub>H_HB</sub>    | Logic 1                   | $2xt_{L_{HB}}$      |     | 360 | μS |

| Low Time High Bit          | $t_{L_{HB}}$         | Logic 1                   | 2                   |     | 180 | μS |

| Acknowledge Output Voltage | V                    | Open Drain,               |                     |     | 0.4 | v  |

| Low                        | V <sub>ACKNL</sub>   | $R_{PULL_{UP}}=15k\Omega$ |                     |     | 0.4 | v  |

| Acknowledge Valid Time     | t <sub>valACKN</sub> | Note 2                    |                     |     | 2   | μS |

| Duration of Acknowledge    | +                    | Note 2                    |                     |     | 512 |    |

| Condition                  | t <sub>ACKN</sub>    | NOLE 2                    |                     |     | 512 | μS |

| Thermal Shutdown           |                      |                           |                     |     |     |    |

| Thermal Shutdown           | T <sub>SD</sub>      |                           |                     | 160 |     | °C |

| Temperature                | I SD                 |                           |                     | 100 |     | C  |

| T <sub>SD</sub> Hysteresis | T <sub>SD-HYS</sub>  |                           |                     | 30  |     | °C |

| Shutdown Delay             | t <sub>SHDN</sub>    |                           |                     |     |     | ms |

**Note 1:** To enter in 1-wire digital dimming mode, the EN pin has to be low for more than  $t_{1W_DET}$  during  $t_{1W-WIN}$ **Note 2:** Acknowledge condition active 0, this condition will only be applied in case the RFA bit is set. Open drain output, line needs to be pulled high by the host with resistor load

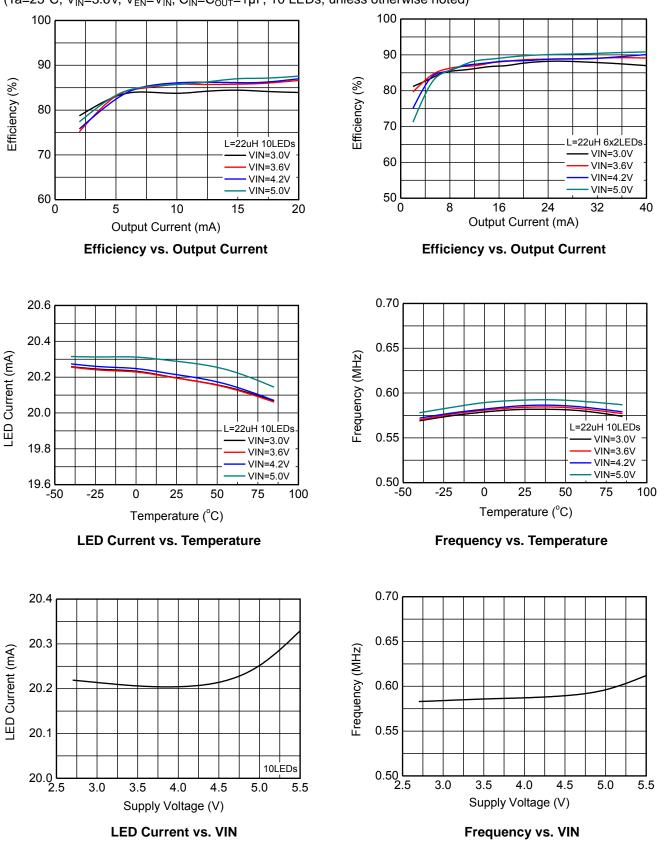

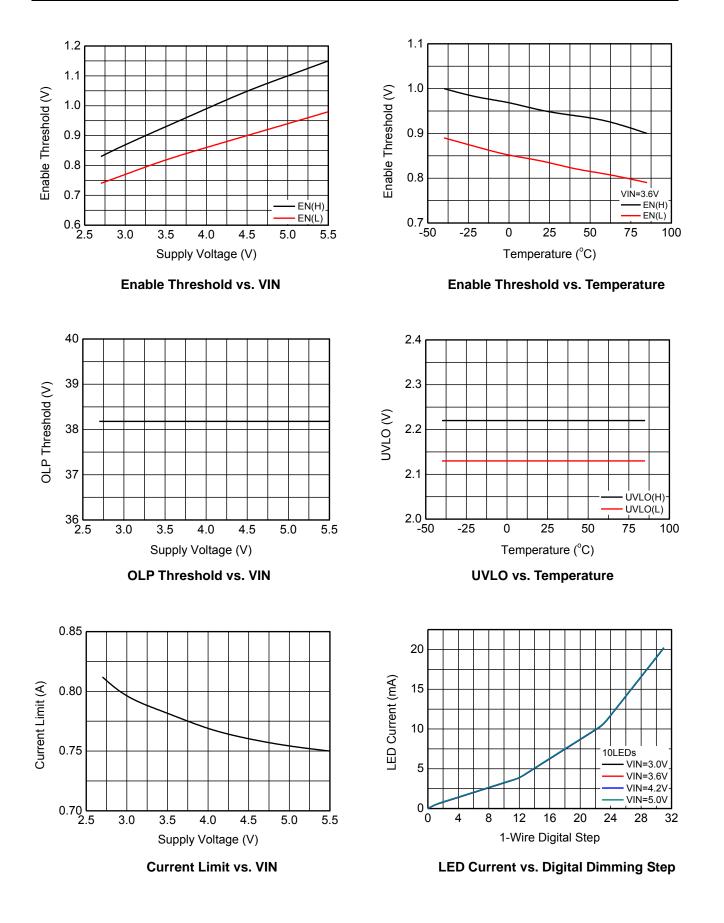

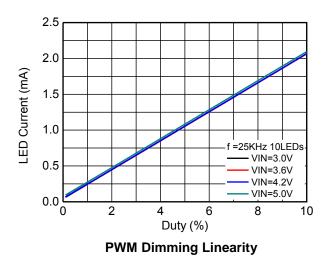

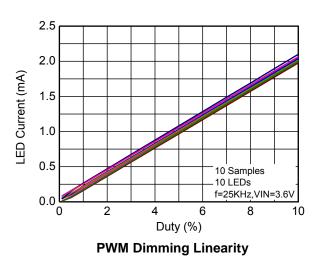

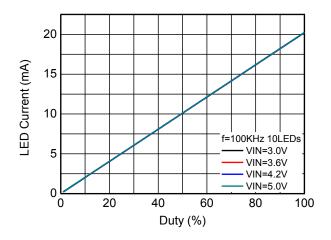

# **Typical Characteristics**

(Ta=25°C, V<sub>IN</sub>=3.6V, V<sub>EN</sub>=V<sub>IN</sub>, C<sub>IN</sub>=C<sub>OUT</sub>=1 $\mu$ F, 10 LEDs, unless otherwise noted)

WD3138

**PWM Dimming Linearity**

**PWM Dimming Linearity**

**PWM Dimming Linearity**

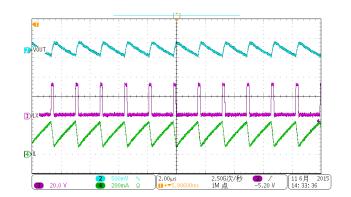

**Operation Waveforms**

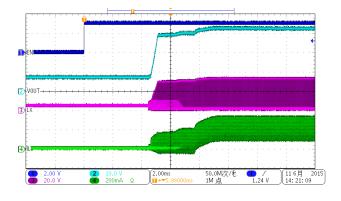

WD3138

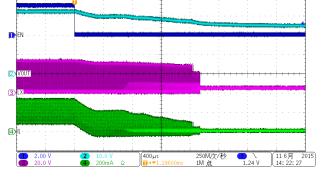

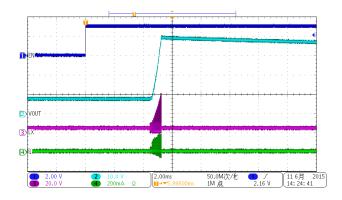

Start-Up from EN

Te<u>k 预览</u>

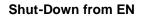

Start-Up from VIN

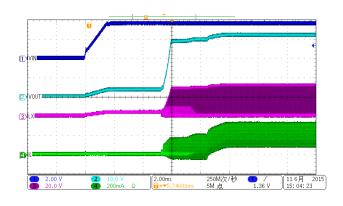

Start-Up with LED Open

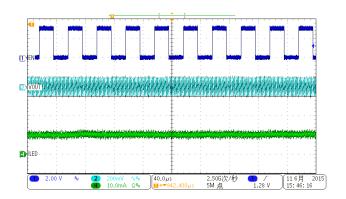

**PWM Dimming Waveforms**

## **Operation Information**

### Operation

The WD3138 is a high efficiency, high output voltage boost converter in a small package size. The device is ideal for driving white LED in series. The serial LED connection provides even illumination by sourcing the same output current through all LEDs, eliminating the need for expensive factory calibration. The device integrates 40V/0.8A switch FET and operates in pulse width modulation (PWM) with 600kHz fixed switching frequency. For operation see the block diagram. The duty cycle of the converter is set by the error amplifier output and the current signal applied to the PWM control comparator. The control architecture is based on traditional current-mode control; therefore, slope compensation is added to the current signal to allow stable operation for duty cycles larger than 50%. The feedback loop regulates the FB pin to a low reference voltage (200mV typical), reducing the power dissipation in the current sense resistor.

### Soft Start-up

Soft-start circuitry is integrated into the IC to avoid a high inrush current during start-up. After the device is enabled, the voltage at FB pin ramps up to the reference voltage in 32 steps with each step taking 213us. This ensures that the output voltage rises slowly to reduce the input current. Additionally, for the first 5msec after the COMP voltage ramps, the current limit of the switch is set to half of the normal current limit spec. During this period, the input current is kept below 400mA (typical). See the start-up waveform of a typical example.

### **Open LED Protection**

Open LED protection circuitry prevents IC damage as the result of white LED disconnection. The WD3138 monitors the voltage at the LX pin and FB pin during each switching cycle. The circuitry turns off the switch FET and shuts down the IC when both of the following conditions persist for 8 switching clock cycles: (1) the LX voltage exceeds the VovP threshold and (2) the FB voltage is less than half of regulation voltage. Then, the WD3138 turns off the power switch FET and shuts down IC until EN or power supply is recycled to enable IC.

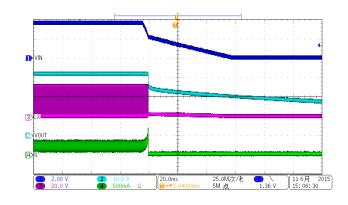

### Shutdown

The WD3138 enters shutdown mode when the EN voltage is logic low for more than 2.5ms. During shutdown, the input supply current for the device is less than 1 $\mu$ A (max). Although the internal FET does not switch in shutdown, there is still a DC current path between the input and the LEDs through the inductor and Schottky diode. The minimum forward voltage of the LED array must exceed the maximum input voltage to ensure that the LEDs remain off in shutdown. However, in the typical application with two or more LEDs, the forward voltage is large enough to reverse bias the Schottky and keep leakage current low.

### **Current Program**

The FB voltage is regulated by a low 0.2V reference voltage. The LED current is programmed externally using a current-sense resistor in series with the LED string. The value of the  $R_{SET}$  is calculated using Equation 1:

$$I_{LED} = \frac{V_{FB}}{R_{SET}} = \frac{200 \text{mV}}{R_{SET}}$$

(1)

Where

$I_{LED}$  = output current of LEDs  $V_{FB}$  = regulated voltage of FB  $R_{SET}$  = current sense resistor

The output current tolerance depends on the FB accuracy and the current sensor resistor accuracy.

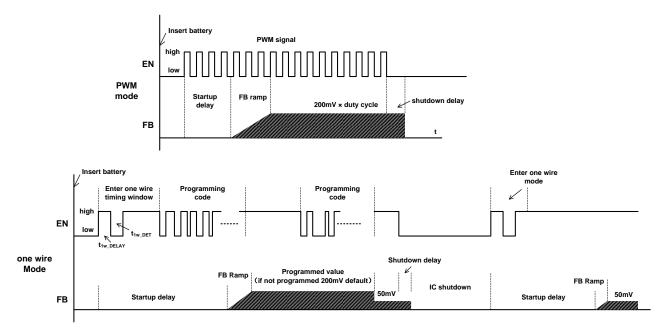

### LED Brightness Dimming Mode Selection

The EN pin is used for the control input for both dimming modes: PWM dimming and 1 wire dimming. The dimming mode for the WD3138 is selected each time the device is enabled. The default

# ݕ 🗤 SEMI

dimming mode is PWM dimming. To enter the 1 wire mode, the following digital pattern on the EN pin must be recognized by the IC every time the IC starts from the shutdown mode.

- 1. Pull EN pin high to enable the WD3138, and to start the 1 wire detection window.

- 2. After the 1 wire detection delay  $(t_{1W\_DELAY}, 100us)$  expires, drive EN low for more than the 1 wire detection time  $(t_{1W\_DET}, 260us)$ .

- The EN pin has to be low for more than 1 wire detection time before the 1 wire detection window (t<sub>1W\_WIN</sub>, 1ms) expires. 1 wire detection window starts from the first EN pin low to high transition.

The IC immediately enters the 1 wire mode once the above three conditions are met. The 1 wire communication can start before the detection window expires. Once the dimming mode is programmed, it cannot be changed without another start up. This means the IC needs to be shut down by pulling the EN low for 2.5ms and restart. See the *Dimming Mode Detection and Soft Start* (Figure 1) for a graphical explanation.

### **PWM Brightness Dimming**

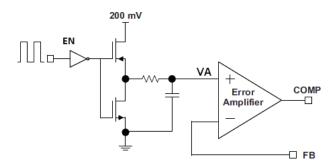

When the EN pin is constantly high, the FB voltage is regulated to 200mV typically. However, the EN pin allows a PWM signal to reduce this regulation voltage; therefore, it achieves LED brightness dimming. The relationship between the duty cycle and FB voltage is given by Equation 2.

$$V_{\rm FB} = {\rm Duty} \times 200 {\rm mV}$$

(2)

Where

Duty = Duty Cycle of the PWM signal 200mV = Internal Reference Voltage

As shown in Figure 2, the IC chops up the internal 200mV reference voltage at the duty cycle of the PWM signal. The pulse signal is then filtered by an internal low pass filter. The output of the filter is connected to the error amplifier as the reference voltage for the FB pin regulation. Therefore, although a PWM signal is used for brightness dimming, only the WLED DC current is modulated, which is often referred as analog dimming.

Figure 1. Dimming Mode Detection and Soft Start PWM Brightness Dimming

# WD3138

This eliminates the audible noise which often occurs when the LED current is pulsed in replica of the frequency and duty cycle of PWM control. Unlike other scheme which filters the PWM signal for analog dimming, WD3138 regulation voltage is independent of the PWM logic voltage level which often has large variations.

Figure 2. Block Diagram of Programmable FB Voltage Using PWM Signal

For optimum performance, use the PWM dimming frequency in the range of 5kHz to 100kHz. And the recommended minimum PWM Duty Cycle is 1% for stable LED driving and no blind dimming.

### 1-wire Digital Brightness Dimming

The EN pin features a simple digital interface to allow digital brightness control. The digital dimming can save the processor power and battery life as it does not require a PWM signal all the time, and the processor can enter idle mode if available.

The WD3138 adopts the 1-wire digital interface for the digital dimming, which can program the FB voltage to any of the 32 steps with single command. The step increment increases with the voltage to produce pseudo logarithmic curve for the brightness step. See the Table 1 for the FB pin voltage steps. The default step is full scale when the device is first enabled (VFB = 200 mV). The programmed reference voltage is stored in an internal register. A power reset clears the register value and reset it to default.

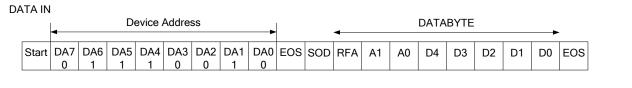

1 wire digital interface is a simple but flexible one pin interface to configure the FB voltage. The interface is based on a master-slave structure, where the master is typically a microcontroller or application processor. Figure 3 and Table 2 give an overview of the protocol. The protocol consists of a device specific address byte and a data byte. The device specific address byte is fixed to 72 hex. The data byte consists of five bits for information, two address bits, and the RFA bit. The RFA bit set to high indicates the *Request for Acknowledge* condition. The Acknowledge condition is only applied if the protocol was received correctly. The advantage of 1-wire digital interface compared with other on pin interfaces is that its bit detection is in a large extent independent from the bit transmission rate.

|    | FB voltage<br>(mV) | D4 | D3 | D2 | D1 | D0 |

|----|--------------------|----|----|----|----|----|

| 0  | 0                  | 0  | 0  | 0  | 0  | 0  |

| 1  | 5                  | 0  | 0  | 0  | 0  | 1  |

| 2  | 8                  | 0  | 0  | 0  | 1  | 0  |

| 3  | 11                 | 0  | 0  | 0  | 1  | 1  |

| 4  | 14                 | 0  | 0  | 1  | 0  | 0  |

| 5  | 17                 | 0  | 0  | 1  | 0  | 1  |

| 6  | 20                 | 0  | 0  | 1  | 1  | 0  |

| 7  | 23                 | 0  | 0  | 1  | 1  | 1  |

| 8  | 26                 | 0  | 1  | 0  | 0  | 0  |

| 9  | 29                 | 0  | 1  | 0  | 0  | 1  |

| 10 | 32                 | 0  | 1  | 0  | 1  | 0  |

| 11 | 35                 | 0  | 1  | 0  | 1  | 1  |

| 12 | 38                 | 0  | 1  | 1  | 0  | 0  |

| 13 | 44                 | 0  | 1  | 1  | 0  | 1  |

| 14 | 50                 | 0  | 1  | 1  | 1  | 0  |

| 15 | 56                 | 0  | 1  | 1  | 1  | 1  |

| 16 | 62                 | 1  | 0  | 0  | 0  | 0  |

| 17 | 68                 | 1  | 0  | 0  | 0  | 1  |

| 18 | 74                 | 1  | 0  | 0  | 1  | 0  |

| 19 | 80                 | 1  | 0  | 0  | 1  | 1  |

| 20 | 86                 | 1  | 0  | 1  | 0  | 0  |

| 21 | 92                 | 1  | 0  | 1  | 0  | 1  |

| 22 | 98                 | 1  | 0  | 1  | 1  | 0  |

| 23 | 104                | 1  | 0  | 1  | 1  | 1  |

| 24 | 116                | 1  | 1  | 0  | 0  | 0  |

| 25 | 128                | 1  | 1  | 0  | 0  | 1  |

| 26 | 140                | 1  | 1  | 0  | 1  | 0  |

| 27 | 152                | 1  | 1  | 0  | 1  | 1  |

| 28 | 164                | 1  | 1  | 1  | 0  | 0  |

| 29 | 176                | 1  | 1  | 1  | 0  | 1  |

| 30 | 188                | 1  | 1  | 1  | 1  | 0  |

| 31 | 200                | 1  | 1  | 1  | 1  | 1  |

Table 1. Selectable FB Voltage

| Table 2. | One Wire Digital Interface Bit Description |

|----------|--------------------------------------------|

|----------|--------------------------------------------|

| BYTE      | BIT                | NAME | TRANSMISSION | DESCRIPTION                                                             |  |  |

|-----------|--------------------|------|--------------|-------------------------------------------------------------------------|--|--|

| BIIC      | NUMBER             | NAME | DIRECTION    | DESCRIPTION                                                             |  |  |

|           | 7                  | DA7  |              | 0 MSB device address                                                    |  |  |

|           | 6                  | DA6  |              | 1                                                                       |  |  |

| DEVICE    | 5                  | DA5  |              | 1                                                                       |  |  |

| ADDRESS   | 4                  | DA4  | INI          | 1                                                                       |  |  |

| BYTE      | 3                  | DA3  | IN           | 0                                                                       |  |  |

| 72 hex    | 2                  | DA2  |              | 0                                                                       |  |  |

|           | 1                  | DA1  |              | 1                                                                       |  |  |

|           | 0                  | DA0  |              | 0 LSB device address                                                    |  |  |

|           | 7(MSB)             | RFA  |              | Request for acknowledge. If high, acknowledge is applied by device      |  |  |

|           | 6                  | A1   |              | 0 Address bit 1                                                         |  |  |

|           | 5                  | A0   |              | 0 Address bit 0                                                         |  |  |

| Data buta | 4 D4   3 D3   2 D2 |      | IN           | Data bit 4                                                              |  |  |

| Data byte |                    |      | IIN          | Data bit 3                                                              |  |  |

|           |                    |      |              | Data bit 2                                                              |  |  |

|           | 1                  | D1   |              | Data bit 1                                                              |  |  |

|           | 0(LSB)             | D0   |              | Data bit 0                                                              |  |  |

|           |                    |      |              | Acknowledge condition active 0, this condition will only be applied in  |  |  |

|           |                    |      |              | case RFA bit is set. Open drain output, Line needs to be pulled high by |  |  |

|           |                    | ACK  | OUT          | the host with a pull-up resistor. This feature can only be used if the  |  |  |

|           |                    |      |              | master has an open drain output stage. In case of a pull output stage   |  |  |

|           |                    |      |              | Acknowledge condition may not be requested!                             |  |  |

DATA OUT ACK

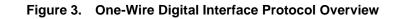

#### 1 wire Brightness Timing, without Acknowledge RFA=0

Figure 4. One-Wire Digital Interface -- Bit Coding

All bits are transmitted MSB first and LSB last. Figure 4 shows the protocol without acknowledge request (Bit RFA = 0), Figure 4 with acknowledge (Bit RFA = 1) request. Prior to both bytes, device address byte and data byte, a start condition must be applied. For this, the EN pin must be pulled high for at least t<sub>start</sub> (2µs) before the bit transmission starts with the falling edge. If the EN pin is already at high level, no start condition is needed prior to the device address byte. The transmission of each byte is closed with an End of Stream condition for at least tEOS (2µs).

The bit detection is based on a Logic Detection scheme, where the criterion is the relation between tLOW and tHIGH. It can be simplified to:

High Bit: thigh  $\geq$  tLow, but with thigh at least 2x tLow,

#### see Figure 4

Low Bit: thigh < tLow, but with tLow at least 2x thigh, see Figure 4

The bit detection starts with a falling edge on the EN pin and ends with the next falling edge. Depending on the relation between thigh and thow, the logic 0 or 1 is detected.

The acknowledge condition is only applied if:

- Acknowledge is requested by a set RFA bit.

- The transmitted device address matches with the device address of the device.

- 16 bits is received correctly.

If the device turns on the internal ACKN-MOSFET and pulls the EN pin low for the time tACKN, which is

512µs maximum then the Acknowledge condition is valid after an internal delay time tvalACK. This means that the internal ACKN-MOSFET is turned on after tvalACK, when the last falling edge of the protocol was detected. The master controller keeps the line low in this period. The master device can detect the acknowledge condition with its input by releasing the EN pin after tvalACK and read back a logic 0. The EN pin can be used again after the acknowledge condition ends.

Note that the acknowledge condition may only be requested in case the master device has an open drain output. For a push-pull output stage, the use a series resistor in the EN line to limit the current to 500µA is recommended to for such cases as:

- An accidentally requested acknowledge, or

- To protect the internal ACKN-MOSFET.

#### **Under-Voltage Lockout**

An under-voltage lockout prevents operation of the device at input voltages below typical 2.2V. When the input voltage is below the under voltage threshold, the device is shut down and the internal switch FET is turned off. If the input voltage rises by under voltage lockout hysteresis, the IC restarts.

#### **Thermal Shutdown**

An internal thermal shutdown turns off the device when the typical junction temperature of 160°C is exceeded. The device is released from shutdown automatically when the junction temperature decreases by 30°C.

## **Application Information**

#### Maximum Output Current

The overcurrent limit in a boost converter limits the maximum input current and thus maximum input power for a given input voltage. Maximum output power is less than maximum input power due to power conversion losses. Therefore, the current limit setting, input voltage, output voltage and efficiency can all change maximum current output. The current limit clamps the peak inductor current; therefore, the ripple has to be subtracted to derive maximum DC current. The ripple current is a function of switching frequency, inductor value and duty cycle. The following equations take into account of all the above factors for maximum output current calculation.

$$I_{p} = \frac{1}{L \times F_{s} \times \left(\frac{1}{V_{out} + V_{f} - V_{in}} + \frac{1}{V_{in}}\right)}$$

(3)

Where

$I_P$  = inductor peak to peak ripple

L = inductor value

V<sub>f</sub> = Schottky diode forward voltage

F<sub>s</sub> = switching frequency

$V_{\text{out}}$  = output voltage of the boost converter. It is equal to the sum of  $V_{\text{FB}}$  and the voltage drop across LEDs.

$$I_{out\_max} = \frac{V_{in} \times (I_{lim} - I_p/2) \times \eta}{V_{out}}$$

(4)

Where

$I_{out\_max}$  = maximum output current of the boost converter

$l_{lim} = over current limit$  $\eta = efficiency$

### **Inductor Selection**

The selection of the inductor affects steady state operation as well as transient behavior and loop stability. These factors make it the most important

# SEMI

component in power regulator design. There are three important inductor specifications, inductor value, DC resistance and saturation current. Considering inductor value alone is not enough.

The inductor value determines the inductor ripple current. Choose an inductor that can handle the necessary peak current without saturating, according to half of the peak-to-peak ripple current given by Equation 3, pause the inductor DC current given by:

$$I_{in_{DC}} = \frac{V_{out} \times I_{out}}{V_{in} \times \eta}$$

(5)

Inductor values can have  $\pm 20\%$  tolerance with no current bias. When the inductor current approaches saturation level, its inductance can decrease 20% to 35% from the 0A value depending on how the inductor vendor defines saturation current. Using an inductor with a smaller inductance value forces discontinuous PWM when the inductor current ramps down to zero before the end of each switching cycle. This reduces the boost converter's maximum output current, causes large input voltage ripple and reduces efficiency. Large inductance value provides much more output current and higher conversion efficiency. For these reasons, a 10µH to 22µH inductor value range is recommended. A 22µH inductor optimized the efficiency for most application while maintaining low inductor peak to peak ripple. When recommending inductor value, the factory has considered - 40% and +20% tolerance from its nominal value.

### **Schottky Diode Selection**

The rectifier diode supplies current path to the inductor when the internal MOSFET is off. Use a schottky with low forward voltage to reduce losses. The diode should be rated for a reverse blocking voltage greater than the output voltage used. The average current rating must be greater than the maximum load current expected, and the peak current rating must be greater than the peak inductor current.

Diode the following requirements:

- Low forward voltage

- High switching speed : 50ns max.

- Reverse voltage :  $V_{OUT} + V_F$  or more

- Rated current : I<sub>PK</sub> or more

### **Compensation Capacitor Selection**

The compensation capacitor  $C_{COMP}$ , connected from COMP pin to GND, is used to stabilize the feedback loop of the WD3138. A 220nF ceramic capacitor for  $C_{COMP}$  is suitable for most applications.

#### Input and Output Capacitor Selection

The output capacitor is mainly selected to meet the requirements for the output ripple and loop stability. This ripple voltage is related to the capacitor's capacitance and its equivalent series resistance (ESR). Assuming a capacitor with zero ESR, the minimum capacitance needed for a given ripple can be calculated by

$$C_{out} = \frac{(V_{out} - V_{in}) I_{out}}{V_{out} \times F_{s} \times V_{ripple}}$$

(6)

Where, V<sub>ripple</sub> = peak-to-peak output ripple. The additional output ripple component caused by ESR is calculated using:

$$V_{ripple\_ESR} = I_{out} \times R_{ESR}$$

(7)

Due to its low ESR, V<sub>ripple\_ESR</sub> can be neglected for ceramic capacitors, but must be considered if tantalum or electrolytic capacitors are used.

Care must be taken when evaluating a ceramic capacitor's derating under dc bias, aging and AC signal. For example, larger form factor capacitors (in 1206 size) have a resonant frequency in the range of the switching frequency. So the effective capacitance is significantly lower. The DC bias can also significantly reduce capacitance. Ceramic capacitors can loss as much as 50% of its

capacitance at its rated voltage. Therefore, leave the margin on the voltage rating to ensure adequate capacitance at the required output voltage.

The capacitor in the range of  $1\mu$ F to  $10\mu$ F is recommended for input side. The output requires a capacitor in the range of  $0.47\mu$ F to  $10\mu$ F. The output capacitor affects the loop stability of the boost regulator. If the output capacitor is below the range, the boost regulator can potentially become unstable. For example, if use the output capacitor of  $0.1\mu$ F, a 470nF compensation capacitor has to be used for the loop stable.

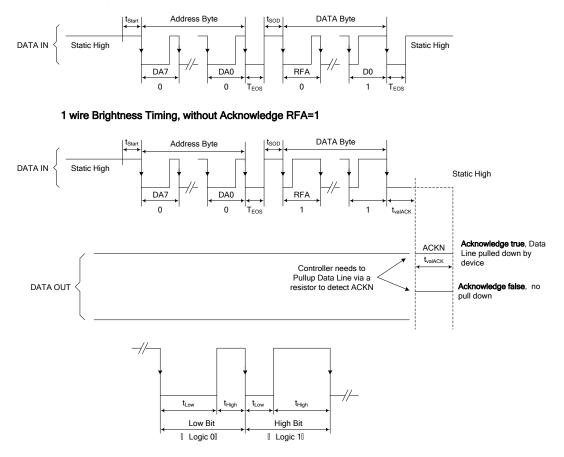

# Layout Consideration

As for all switching power supplies, especially those high frequency and high current ones, layout is an important design step. If layout is not carefully done, the regulator could suffer from instability as well as noise problems. To reduce switching losses, the LX pin rise and fall times are made as short as possible. To prevent radiation of high frequency resonance problems, proper layout of the high frequency switching path is essential. Minimize the length and area of all traces connected to the LX pin and always use a ground plane under the switching regulator to minimize inter-plane coupling. The loop including the PWM switch, Schottky diode, and output capacitor, contains high current rising and falling in nanosecond and should be kept as short as possible. The input capacitor needs not only to be close to the VIN pin, but also to the GND pin in order to reduce the IC supply ripple. Figure 5 shows a sample layout.

Figure 5. Sample Layout

## **Thermal consideration**

The maximum IC junction temperature should be restricted to  $125^{\circ}$ C under normal operating conditions. This restriction limits the power dissipation of the WD3138. Calculate the maximum allowable dissipation, P<sub>D(max)</sub>, and keep the actual dissipation less than or equal to P<sub>D(max)</sub>. The maximum-power-dissipation limit is determined using Equation 8:

$$P_{D(max)} = \frac{125^{\circ}C - T_{A}}{R_{\theta JA}}$$

(8)

Where,  $T_A$  is the maximum ambient temperature for the application. ReJA is the thermal resistance junction-to-ambient given in Power Dissipation Table.

The WD3138 comes in DFN packages. Compared with the TSOT package, the DFN package has

better heat dissipation. This package includes a thermal pad that improves the thermal capabilities of the package. The  $\theta_{JA}$  of the DFN package greatly depends on the PCB layout and thermal pad connection. The thermal pad must be soldered to the analog ground on the PCB. Using thermal vias underneath the thermal pad as illustrated in the layout example.

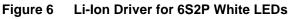

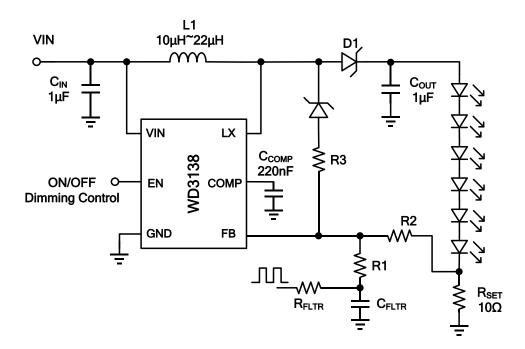

# **Additional Typical Applications**

Figure 7 Li-Ion Driver for 6 White LEDs with External PWM Dimming Network

Figure 8 Li-Ion Driver for 8 White LED

/// SEMI

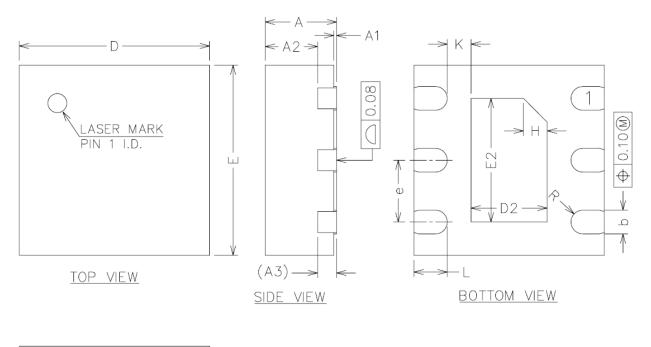

# Package outline dimensions

DFN-2x2-6L

<u>SIDE VIEW</u>

| Symbol | Dimensions in millimeter |          |      |  |  |

|--------|--------------------------|----------|------|--|--|

| Зушой  | Min.                     | Nom.     | Max. |  |  |

| A      | 0.70                     | 0.75     | 0.80 |  |  |

| A1     | 0.00                     | 0.02     | 0.05 |  |  |

| A2     | 0.5                      | 0.55     | 0.6  |  |  |

| A3     |                          | 0.20 REF |      |  |  |

| b      | 0.20                     | 0.25     | 0.30 |  |  |

| D      | 1.90                     | 2.00     | 2.10 |  |  |

| E      | 1.90                     | 2.00     | 2.10 |  |  |

| D2     | 0.70                     | 0.80     | 0.90 |  |  |

| E2     | 1.20                     | 1.30     | 1.40 |  |  |

| е      | 0.55                     | 0.65     | 0.75 |  |  |

| Н      | 0.25 REF                 |          |      |  |  |

| К      | 0.20                     | —        | —    |  |  |

| L      | 0.30                     | 0.35     | 0.40 |  |  |

| R      | 0.11                     | _        | —    |  |  |